## 54F/74F412

# Multi-Mode Buffered Latch With 3-State Outputs

#### Description

The 'F412 is an 8-bit latch with 3-state output buffers. Also included is a status flip-flop for providing device-busy or request-interrupt commands. Separate Mode and Select inputs allow data to be stored with the outputs enabled or disabled. The device can also operate in a fully transparent mode. The 'F412 is the functional equivalent of the Intel 8212.

- 3-State Outputs

- Status Flip-flop for Interrupt Commands

- Asynchronous or Latched Receiver Modes

- 300 mil 24-Pin Slim Package

Ordering Code: See Section 5

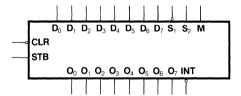

#### **Logic Symbol**

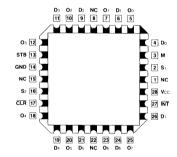

#### **Connection Diagrams**

# Pin Assignment for DIP and SOIC

Pin Assignment for LCC and PCC

#### Input Loading/Fan-Out: See Section 3 for U.L. definitions

| Pin Names                             | Description        | <b>54F/74F(U.L.)</b><br>HIGH/LOW |

|---------------------------------------|--------------------|----------------------------------|

| O <sub>0</sub> -O <sub>7</sub>        | Latch Outputs      | 75/15 (12.5)                     |

| $D_0$ - $D_7$                         | Data Inputs        | 0.5/0.375                        |

| D <sub>0</sub> -D <sub>7</sub><br>CLR | Clear              | 0.5/0.375                        |

| STB                                   | Strobe             | 0.5/0.375                        |

| ĪNT                                   | Interrupt          | 25/12.5                          |

| M                                     | Mode Control Input | 0.5/0.375                        |

| $\overline{S}_1,S_2$                  | Select Inputs      | 0.5/0.375                        |

#### **Functional Description**

This high-performance eight-bit parallel expandable buffer register incorporates package and mode selection inputs and an edge-triggered status flipflop designed specifically for implementing busorganized input/output ports. The 3-state data outputs can be connected to a common data bus and controlled from the appropriate select inputs to receive or transmit data. An integral status flipflop provides busy or request interrupt commands.

The eight data latches are fully transparent when the internal gate enable, G, input is HIGH and the outputs are enabled. Latch transparency is selected by the mode control (M), select ( $\overline{S}_1$  and  $S_2$ ), and the strobe (STB) inputs and during transparency each data output ( $O_n$ ) follows its respective data input ( $D_n$ ). This mode of operation can be terminated by clearing, de-selecting, or holding the data latches.

An input mode or an output mode is selectable from the M input. In the input mode, M = L, the eight data latch inputs are enabled when the strobe is HIGH regardless of device selection. If selected during an input mode, the outputs will follow the data inputs. When the strobe input is taken LOW, the latches will store the most-recently setup data.

In the output mode, M = H, the output buffers are enabled regardless of any other control input. During the output mode the content of the register is under control of the select ( $\overline{S}_1$  and  $S_2$ ) inputs.

#### **Data Latches Function Table**

| Function  | CLR    | M      | <u>S</u> 1 | S <sub>2</sub> | STB    | Data In | Data Out                         |

|-----------|--------|--------|------------|----------------|--------|---------|----------------------------------|

| Clear     | L<br>L | H<br>L | H<br>L     | X              | X<br>L | X<br>X  | L<br>L                           |

| De-select | X<br>X | L<br>L | X<br>H     | L<br>X         | X<br>X | X<br>X  | Z<br>Z                           |

| Hold      | Н      | H<br>L | H<br>L     | L<br>H         | X<br>L | X<br>X  | Q <sub>0</sub><br>Q <sub>0</sub> |

| Data Bus  | H      | H      | L<br>L     | H              | X<br>X | L<br>H  | L<br>H                           |

| Data Bus  | H      | L<br>L | L<br>L     | H              | H      | L<br>H  | L<br>H                           |

#### Status Flip-flop Function Table

| CLR | CLR S <sub>1</sub> S <sub>2</sub> |   | STB | ĪNT |

|-----|-----------------------------------|---|-----|-----|

| L   | Н                                 | Х | Х   | н   |

| L   | X                                 | L | Χ   | Н   |

| Н   | Ιx                                | Х | 7   | L   |

| Н   | L                                 | Н | X   | L   |

H = HIGH Voltage Level

L = LOW Voltage Level

X = Immaterial

Z = High Impedance

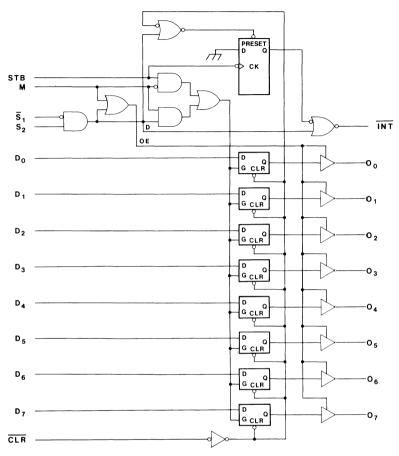

#### **Logic Diagram**

Please note that this diagram is provided only for the understanding of logic operations and should not be used to estimate propagation delays.

DC Characteristics over Operating Temperature Range (unless otherwise specified)

| Symbol                                                   | Parameter            |     | 54F/74F        |                |       |                       |  |

|----------------------------------------------------------|----------------------|-----|----------------|----------------|-------|-----------------------|--|

|                                                          |                      | Min | Тур            | Max            | Units | Conditions            |  |

| I <sub>CCH</sub><br>I <sub>CCL</sub><br>I <sub>CCZ</sub> | Power Supply Current |     | 33<br>40<br>40 | 50<br>60<br>60 | mA    | V <sub>CC</sub> = Max |  |

### AC Characteristics: See Section 3 for waveforms and load configurations

|                                      | Parameter                                                       | 54F/74F                                                    | 54F                        | 74F                                    | Units | Fig.<br>No.         |

|--------------------------------------|-----------------------------------------------------------------|------------------------------------------------------------|----------------------------|----------------------------------------|-------|---------------------|

| Symbol                               |                                                                 | $T_A = +25^{\circ}C$ $V_{CC} = +5.0$ $C_L = 50 \text{ pF}$ | 1 7 00                     | $T_A$ , $V_{CC} =$ $Com$ $C_L = 50 pF$ |       |                     |

|                                      |                                                                 | Min Typ Ma                                                 | ax Min Max                 | Min Max                                |       |                     |

| t <sub>PLH</sub>                     | Propagation Delay D <sub>n</sub> to O <sub>n</sub>              |                                                            | 3.0 11.5<br>5.5 2.0 8.5    | 3.0 9.5<br>2.0 7.5                     | ns    | 3-1<br>3-4          |

| t <sub>PLH</sub>                     | Propagation Delay $\overline{S}_1$ , $S_2$ or STB to $O_n$      | 8.5 14.5 18<br>7.5 12.5 16                                 | i i                        | 7.5 20.5<br>6.5 17.5                   | ns    | 3-1<br>3-7          |

| t <sub>PLH</sub><br>t <sub>PHL</sub> | Propagation Delay $\overline{S}_1$ or $S_2$ to $\overline{INT}$ | 4.5 7.5 9<br>4.5 8.0 10                                    | .5 3.5 12.0<br>.5 3.5 12.5 | 4.0 10.5<br>4.0 11.5                   | ns    | 3-1<br>3-10         |

| t <sub>PHL</sub>                     | Propagation Delay<br>CLR to O <sub>n</sub>                      | 7.5 12.5 16                                                | .0 5.5 18.5                | 6.5 17.5                               | ns    | 3-1<br>3-9          |

| t <sub>PHL</sub>                     | Propagation Delay<br>STB to INT                                 | 6.5 11.0 14                                                | .0 5.5 17.5                | 5.5 15.0                               | ns    | 3-1<br>3-10         |

| t <sub>PZH</sub><br>t <sub>PZL</sub> | Access Time, HIGH or LOW $\overline{S}_1$ to $O_n$              | 8.0 12.5 18<br>6.5 11.0 14                                 |                            | 7.0 19.0<br>5.5 15.0                   | ns    | 3-1<br>3-12<br>3-13 |

| t <sub>PHZ</sub><br>t <sub>PLZ</sub> | Disable Time, HIGH or LOW $\overline{S}_1$ to $O_n$             | 4.5 8.0 10<br>6.5 11.0 14                                  |                            | 4.0 11.5<br>5.5 15.0                   |       |                     |

| t <sub>PZH</sub><br>t <sub>PZL</sub> | Access Time, HIGH or LOW S <sub>2</sub> to O <sub>n</sub>       | 7.5 12.5 16<br>5.0 9.0 11                                  |                            | 6.5 17.5<br>4.5 12.5                   | ns    | 3-1<br>3-12<br>3-13 |

| t <sub>PHZ</sub>                     | Disable Time, HIGH or LOW S <sub>2</sub> to O <sub>n</sub>      | 4.5 7.5 9<br>5.5 9.5 12                                    | .5 3.5 12.5<br>.0 4.5 14.5 | 4.0 10.5<br>4.5 13.0                   |       |                     |

| t <sub>PZH</sub>                     | Access Time, HIGH or LOW M to O <sub>n</sub>                    | 5.0 8.5 11<br>5.0 8.5 11                                   |                            | 4.5 12.0<br>4.5 12.0                   | ns    | 3-1                 |

| t <sub>PHZ</sub><br>t <sub>PLZ</sub> | Disable Time, HIGH or LOW M to O <sub>n</sub>                   | 4.0 7.0 9<br>5.0 8.5 11                                    | .0 3.5 11.5<br>.0 4.5 14.0 | 3.5 10.0<br>4.5 12.0                   |       | 3-12<br>3-13        |

# AC Operating Requirements: See Section 3 for waveforms

|                                          | Parameter                                                        | 54F/74F                                     | 54F                                | 74F                                       | Units | Fig.<br>No. |

|------------------------------------------|------------------------------------------------------------------|---------------------------------------------|------------------------------------|-------------------------------------------|-------|-------------|

| Symbol                                   |                                                                  | $T_A = +25$ °C<br>$V_{CC} = +5.0 \text{ V}$ | T <sub>A</sub> , V <sub>CC</sub> = | T <sub>A</sub> , V <sub>CC</sub> =<br>Com |       |             |

|                                          |                                                                  | Min Typ Max                                 | Min Max                            | Min Max                                   |       |             |

| t <sub>s</sub> (H)                       | Setup Time, HIGH or LOW $D_n$ to $\overline{S}_1$ , $S_2$ or STB | 0<br>0                                      | 2.0<br>2.0                         | 1.0<br>1.0                                |       | 0.45        |

| t <sub>h</sub> (H)<br>t <sub>h</sub> (L) | Hold Time $D_n$ to $\overline{S}_1$ , $S_2$ or STB               | 8.0<br>8.0                                  | 10.0<br>10.0                       | 9.0<br>9.0                                | ns    | 3-15        |

| t <sub>w</sub> (H)<br>t <sub>w</sub> (L) | \$\overline{S}_1\$, \$S_2\$ or STB Pulse Width, HIGH or LOW      | 8.0<br>8.0                                  | 11.0<br>11.0                       | 9.0<br>9.0                                | ns    | 3-9         |

| t <sub>w</sub> (L)                       | CLR Pulse Width, LOW                                             | 8.0                                         | 11.5                               | 9.0                                       | ns    | 3-9         |